# 1A Low Dropout LDO with Adjustable Output

## **General Description**

The HM6223B series are CMOS-based low-dropout, low-power linear regulators, offering 1A with low dropout voltage, high ripple rejection, high output accuracy and low supply current. The HM6223B consist of an accurate voltage-reference block, an error amplifier, a voltage-setting resistor net, a PMOSFET pass device, a thermal-shutdown circuit, and a current limit circuit with short protection.

The HM6223B series use a type of outstanding CMOS process to minimize the supply current. A low on-resistance PMOS pass device is equipped for lower dropout voltage. HM6223B also possess the CE function to save more energy and extend the battery life.

The HM6223B series can choose the output current 1.0A. The output voltage can be adjusted from 0.75v to 4.3v using two external resistors.

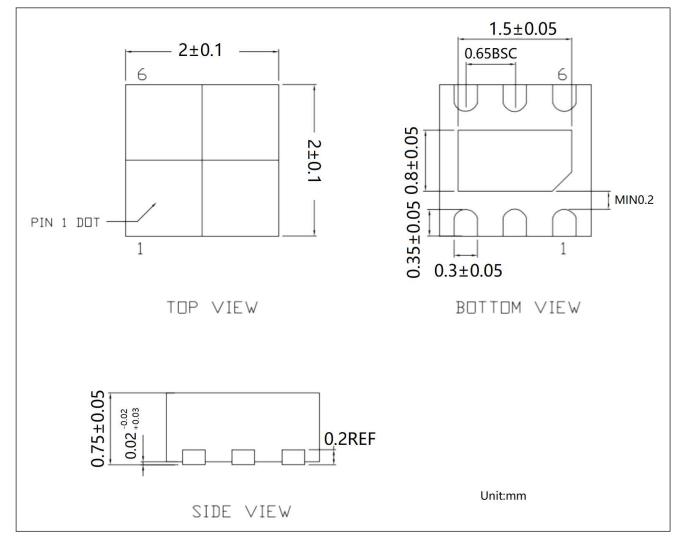

The HM6223B series are available in the DFN6 package (2mm\*2mm).

## Features

- Wide Input Voltage Range: 1.8V to 5.5V

- Output Current: 1.0A optional

- Adjustable Output Voltage Range: 0.75V to 4.3V

- Very Low  $I_Q$ : 110 $\mu$ A

- Excellent Load/Line Transient Response

- Line Regulation: 0.02% typical

- Built-in overcurrent protection and thermal shutdown circuit

- Built-in Auto-discharging circuit

- Reverse Current Protection

- Package: DFN6

## **Applications**

- Constant-voltage power supply for battery-powered device

- Constant-voltage power supply for TV, notebook PC and home electric appliance

- Constant-voltage power supply for portable equipment

- Label Information

#### HM6223B-ADJX

Package specification D: DFN6-2mm\*2mm package P:SOT89-5L package

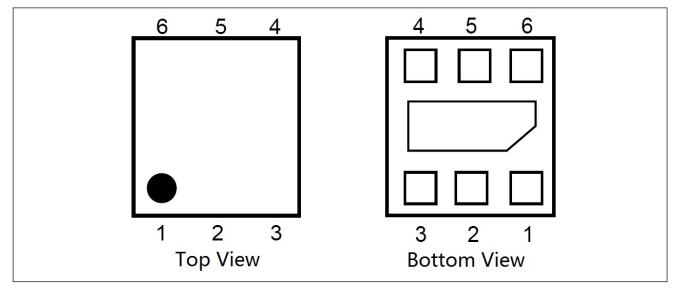

# **Pin Configuration**

## **Pin Function**

| Pin | Symbol | Pin Description                                                                               |  |

|-----|--------|-----------------------------------------------------------------------------------------------|--|

| 1   | VOUT   | Output Pin                                                                                    |  |

| 2   | ADJ    | Adjustable Regulator Feedback Input. Connect to output voltage resistor divider central node. |  |

| 3   | GND    | Ground Pin                                                                                    |  |

| 4   | CE     | Chip Enable Pin                                                                               |  |

| 5   | NC     | No connect                                                                                    |  |

| 6   | VDD    | Input Pin                                                                                     |  |

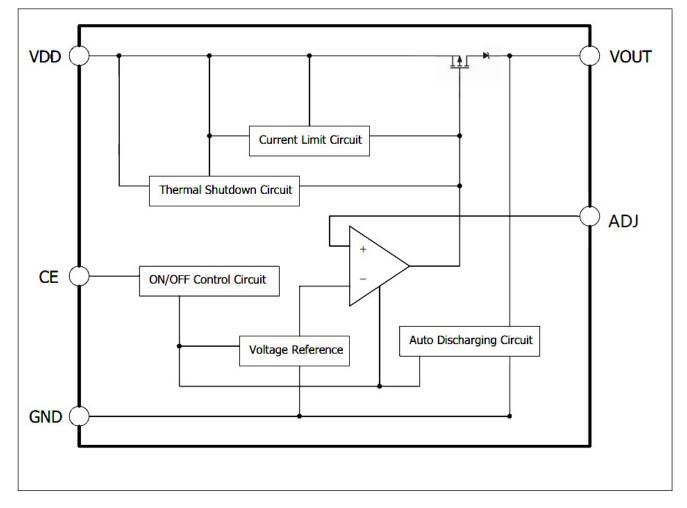

### **Block Diagram**

## **Functional Description**

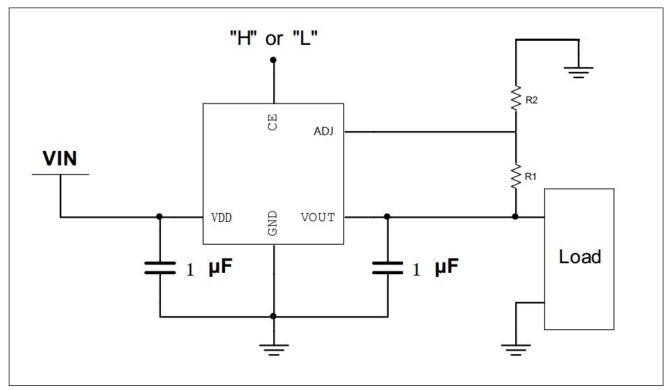

#### **Input Capacitor**

A  $1\mu$ F ceramic capacitor is recommended to connect between V<sub>DO</sub> and GND pins to decouple input power supply glitch and noise. The amount of the capacitance may be increased without limit. This input capacitor must be located as close as possible to the device to assure input stability and less noise. For PCB layout, a wide copper trace is required for both V<sub>IN</sub> and GND.

Please pay attention, in the case of high impedance of the power supply, the input capacitance of the IC is small or the capacitor is not connected, the oscillation may occur. When the capacitance value of the output capacitor is greater than the capacitance value of the input capacitor, it is possible to generate oscillation.

#### **Output Capacitor**

An output capacitor is required for the stability of the LDO. The recommended output capacitance is  $1\mu$ F, ceramic capacitor is recommended, and temperature characteristics are X7R or X5R. Higher capacitance values help to improve load/line transient response. The output capacitance may be increased to keep low undershoot/overshoot. Place output capacitor as close as possible to V<sub>OUT</sub> and GND pins.

#### **CE Pin Operation**

The HM6223B is turned on by setting the CE pin to "H". Since the CE pin is neither pulled down nor pulled up internally, do not set it in floating status. When the CE pin is not used, connect the CE pin with  $V_{DD}$  to keep the LDO in operating mode.

#### **Current Limit Protection**

When output current of  $V_{OUT}$  pin is higher than current limit threshold or the  $V_{OUT}$  pin is direct short to GND, the current limit protection will be triggered and clamp the output current at a predesigned level to prevent over-current and thermal damage. HM6223B output current limit will be 1.4A.

#### **Thermal Shutdown Protection**

Thermal protection disables the output when the junction temperature rises to approximately +155°C, allowing the device to cool down. When the junction temperature reduces to approximately +120°C the output circuit is enabled again. Depending on power dissipation, thermal resistance, and ambient temperature, the thermal protection circuit may cycle on and off. This cycling limits the heat dissipation of the regulator, protecting it from damage due to overheating.

#### **Reverse Current Protection Circuit**

If  $V_{OUT}$  is higher than  $V_{IN}$ , the parasitic diode of Pch output transistor becomes forward direction. As a result, the current flows from  $V_{OUT}$  pin to  $V_{DD}$  pin.

The HM6223B series switches the mode to the reverse current protection mode before  $V_{IN}$  becomes lower than  $V_{OUT}$  by connecting the parasitic diode of Pch output transistor to the backward direction, and connecting the gate to  $V_{OUT}$  pin. As a result, the Pch output transistor is turned off. However, from  $V_{OUT}$  pin to GND pin, via the internal divider resistors, very small current IREV flows.

#### **Auto Discharging**

When the CE pin set to "L", the output circuit will be disable immediately, and the Auto-Discharging circuit will be turned on to discharge the electric charge on output capacitor, and decrease the voltage of  $V_{OUT}$  in very short time. The Auto-Discharging function is optional.

#### **Output Voltage**

The output voltage is adjustable using external 2-resistors. For better performance of the circuit, the R2 value need to be between  $30k\Omega$  and  $100k\Omega$ . The output voltage is calculated by:

$$VOUT = (1+R1/R2)*0.75 (V)$$

## **Absolute Maximum Ratings**

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameter                          | Rating          | Unit |

|------------------------------------|-----------------|------|

| Input Voltage                      | -0.3 to 6       | V    |

| Input Voltage (CE Pin)             | -0.3 to 6       | V    |

| Output Voltage                     | -0.3 to VIN+0.3 | V    |

| Maximum Load Current               | 1000            | mA   |

| Maximum Power Consumption          | 1200            | mW   |

| Operating Junction Temperature     | -40 to 125      | °C   |

| Storage Temperature                | -65 to 150      | °C   |

| Lead Temperature (Soldering, 5sec) | 260             | °C   |

## **Recommended Operating Conditions**

| Symbol          | Item                                                          | Rating     | Unit |

|-----------------|---------------------------------------------------------------|------------|------|

| V <sub>IN</sub> | Input Voltage                                                 | 1.8 to 5.5 | V    |

| Iout            | Output Current                                                | 0 to 1000  | mA   |

| Та              | Operating Ambient Temperature                                 | -40 to 85  | °C   |

| C <sub>IN</sub> | Effective Input Ceramic Capacitor Value                       | 1 to 10    | μF   |

| COUT            | Effective Output Ceramic Capacitor Value                      | 1 to 10    | μF   |

| ESR             | Input and Output Capacitor Equivalent Series Resistance (ESR) | 5 to 100   | mΩ   |

## **Electrical Characteristics**

$(Unless otherwise noted , V_{IN} = V_{SET} + 1.0V, Ta = -40^{\circ}C ~~ \sim 85^{\circ}C ~, C_{IN} = C_{OUT} = 1uF ~(\text{effective capacitance}^{(4)}) ~; Typical values are at V_{IN} = V_{SET} + 1.0V, Ta = 25^{\circ}C)$

| PARAMETER                                                      | SYMBOL                           | TEST CONDITIONS                                                                                                             | MIN   | TYP                     | MAX                     | UNIT          |

|----------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------|-------------------------|-------------------------|---------------|

| Input Voltage Operation Range                                  | $V_{IN}^{(1)}$                   | $V_{IN} \ge V_{SET} + 0.5 V$                                                                                                | 1.8   |                         | 5.5                     | V             |

| Output Voltage                                                 | V <sub>OUT</sub>                 | I <sub>OUT</sub> =1mA,Ta=25℃                                                                                                | ×0.98 |                         | ×1.02                   | V             |

| Output voltage                                                 |                                  | I <sub>OUT</sub> =1mA~1A,Ta=25°C                                                                                            | -30   |                         | +30                     | mV            |

| Dropout Voltage                                                | V <sub>DROP</sub> <sup>(2)</sup> | V <sub>OUT</sub> =3.3V, I <sub>OUT</sub> =1A,<br>V <sub>OUT</sub> dropping to 0.98×V <sub>OUT</sub>                         | 60    | 100                     | 140                     | mV            |

| Supply Quiescent Current                                       | I <sub>Q_ON</sub>                | Active mode: V <sub>CE</sub> =high.<br>I <sub>OUT</sub> =0mA                                                                | 70    | 110                     | 150                     | μA            |

| Supply Shutdown Current                                        | I <sub>Q OFF</sub>               | V <sub>CE</sub> =0V                                                                                                         |       | 1                       | 3                       | μA            |

| Output Voltage Line Regulation                                 | Reg <sub>LINE</sub>              | $V_{SET}+0.5V \le V_{IN} \le 5.5V$ $(V_{IN} \ge 1.8V),$ $I_{OUT} = 10mA$ $(\Delta V_{OUT}/\Delta V_{IN}/V_{OUT})$           |       | 0.02                    | 0.1                     | %/V           |

| Output Voltage Load<br>Regulation                              | Reg <sub>LOAD</sub>              | $\label{eq:Iout} \begin{array}{c} I_{OUT} \text{ from 1mA to 1A} \\ V_{IN} = Vset + 0.5 V ~(~ \Delta ~V_{OUT}) \end{array}$ |       | 5                       | 30                      | mV            |

| Line Transient                                                 | V <sub>TRLN</sub> <sup>(3)</sup> | $V_{OUT}=3.3V$ , $I_{OUT}=1mA$ , $V_{IN}$<br>=4.3V to<br>5.5V in 10us, Ta=25°C                                              |       | 15                      | 30                      | — mv          |

| (The absolute value of the output change)                      | V TRLN                           | $V_{OUT}=3.3V$ , $I_{OUT}=1mA$ , $V_{IN}$<br>=5.5V to<br>4.3V in 10us,Ta=25°C                                               |       | 15                      | 30                      |               |

| Load Transient<br>(The absolute value of the<br>output change) | V <sub>TRLD</sub> <sup>(3)</sup> | V <sub>OUT</sub> =3.3V ,V <sub>IN</sub> =4.3V, I <sub>OUT</sub><br>from 1mA<br>to 1000mA in 10us,Ta=25°C                    |       | 75                      | 120                     | mv            |

|                                                                |                                  | V <sub>OUT</sub> =3.3V,V <sub>IN</sub> =4.3V,I <sub>OUT</sub><br>from 1000mA<br>to 1mA in 10us,Ta=25°C                      |       | 75                      | 120                     |               |

| Output Current                                                 | Iout                             |                                                                                                                             | 1000  |                         |                         | mA            |

| Over Current Limit                                             | I <sub>LMT</sub>                 | V <sub>OUT</sub> =3.3V,V <sub>IN</sub> =4.3V,<br>Ta=25°C                                                                    | 1050  | 1400                    | 1900                    | mA            |

| Short Current Limit                                            | I <sub>SHORT</sub>               | V <sub>OUT</sub> =0V, Ta=25℃                                                                                                | 60    | 130                     | 200                     | mA            |

| Inrush Current Limit                                           | I <sub>RUSH</sub>                | V <sub>OUT</sub> =3.3V,V <sub>IN</sub> =4.3V,<br>Ta=25°C                                                                    | 400   | 600                     | 800                     | mA            |

| Power Supply Rejection Ratio                                   | PSRR <sup>(3)</sup>              | f=1kHz, $C_{OUT}=1\mu F$ ,<br>I <sub>OUT</sub> =20mA,<br>V <sub>IN</sub> =4.3V, Ta =25 °C                                   |       | 70                      |                         | dB            |

| Output Noise                                                   | e <sub>N</sub> <sup>(3)</sup>    | 10Hz to 100kHz, $I_{OUT} =$<br>30mA, $C_{OUT} = 1\mu$ F,<br>Ta =25 °C                                                       |       | 50*<br>V <sub>OUT</sub> | 80*<br>V <sub>OUT</sub> | $\mu V_{RMS}$ |

| EN Low Threshold                                    | VIL                             | V <sub>IN</sub> =1.8 to 5.5V                                   |       |     | 0.3 | V  |

|-----------------------------------------------------|---------------------------------|----------------------------------------------------------------|-------|-----|-----|----|

| EN High Threshold                                   | V <sub>IH</sub>                 | V <sub>IN</sub> =1.8 to 5.5V                                   | 1     |     |     | V  |

| CE Pull-down Current                                | I <sub>CE</sub>                 | V <sub>IN</sub> =4.3V, V <sub>CE</sub> =4.3V,<br>Ta=25°C       |       | 0.3 | 1   | μΑ |

| Output resistance of auto<br>discharge at off state | R <sub>LOW</sub>                | V <sub>EN</sub> =0V,V <sub>IN</sub> =4V,I <sub>OUT</sub> =10mA | 30    | 60  | 100 | Ω  |

| Thermal Shutdown Temperature                        | T <sub>TSD</sub> <sup>(3)</sup> | Junction Temperature Rising                                    | 135   | 155 | 175 | °C |

| Thermal Shutdown Released<br>hysteresis             | T <sub>HYS</sub> <sup>(3)</sup> | Junction Temperature falling from shutdown                     | 20    | 40  | 60  | °C |

|                                                     | HBM                             | Reference:<br>ESDA/JEDEC<br>JS-001-2017                        | ±4000 |     |     | V  |

| ESD                                                 | CDM                             | Reference:<br>ESDA/JEDEC<br>JS-002-2014                        | ±1500 |     |     | V  |

Note (1): Here  $V_{IN}$  means internal circuit can work normal. If  $V_{IN} < V_{OUT}$ , Reverse current protection circuit will work .

Note (2): V<sub>DROP</sub> FT test method: test the V<sub>OUT</sub> voltage at Vset +V<sub>DROPMAX</sub> with output current.

Note (3): Guaranteed by design and characterization. not a FT item.

Note (4): Effective capacitance, including the effect of DC bias, tolerance and temperature.

# **Application Circuits**

# Package Dimension